GRAPE-DRシステム

2PFLOPS実現の方法

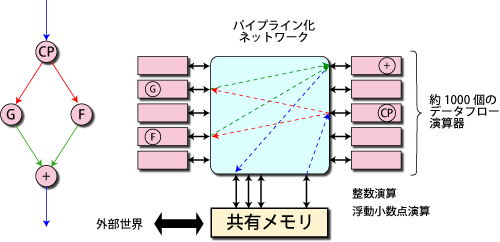

- スタティック・データフロー方式

- データの到着とともに、演算を発火

- 演算プロセッサ間を直接内部ネットワーク結合

- プログラムのデータフローグラフから、演算プロセッサを動的に結合

- 低遅延時間による並列性有効利用

- 高いハードウェア利用効率

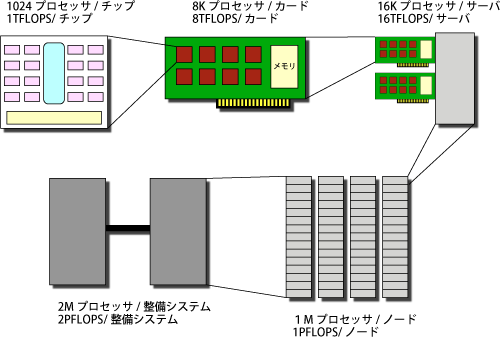

- 1チップ内に1024個の演算プロセッサを実装

- システム全体で、2,097,152個の演算プロセッサ

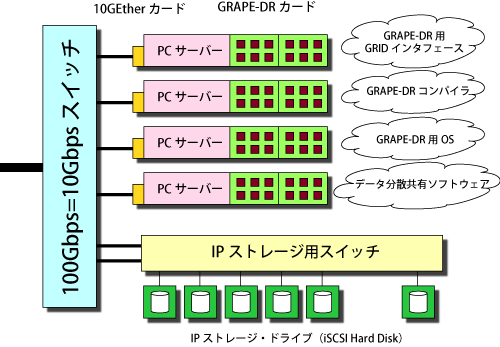

- 汎用サーバの付加プロセッサとして実装

- コンパイラが汎用サーバ上のプログラムとGRAPE-DRプログラムに分割

GRAPE-DRシステムイメージ

GRAPE-DRチップのアーキテクチャ

- スタティック・データフロー技術

- 多数の演算器をパイプライン接続

- 共有メモリと、ネットワーク・パイプラインで接続

- 演算器間の直接接続により細粒度並列処理を実現

- 低遅延時間・高密度実装の実現

GRAPE-DRのアーキテクチャ階層